| Set | Tag | PPN | Valid |

|-----|-----|-----|-------|-----|-----|-------|-----|-----|-------|-----|-----|-------|

| 0   | 03  | -   | 0     | 09  | 0D  | 1     | 00  |     | 0     | 07  | 02  | 1     |

| 1   | 03  | 2D  | 1     | 02  | 1-1 | 0     | 04  | 1-1 | 0     | 0A  | _   | 0     |

| 2   | 02  |     | 0     | 80  | 1-1 | 0     | 06  | 1-  | 0     | 03  | -   | 0     |

| 3   | 07  |     | 0     | 03  | 0D  | 1     | 0A  | 34  | 1     | 02  |     | 0     |

(a) TLB: 4 sets, 16 entries, 4-way set associative

| VPN | PPN | Valid | VPN | PPN | Valid |

|-----|-----|-------|-----|-----|-------|

| 00  | 28  | 1     | 08  | 13  | 1     |

| 01  |     | 0     | 09  | 17  | 1     |

| 02  | 33  | 1     | OA  | 09  | 1     |

| 03  | 02  | 1     | 0B  | -   | 0     |

| 04  | Ţ   | 0     | 0C  | 1   | 0     |

| 05  | 16  | 1     | 0D  | 2D  | 1     |

| 06  | 1—1 | 0     | 0E  | 11  | 1     |

| 07  | -   | 0     | 0F  | 0D  | 1     |

|     |     |       |     |     |       |

(b) Page table: Only the first 16 PTEs are shown

| ldx | Tag | Valid | Blk 0   | Blk 1            | Blk 2 | Blk 3 |

|-----|-----|-------|---------|------------------|-------|-------|

| 0   | 19  | 1     | 99      | 11               | 23    | 11    |

| 1   | 15  | 0     |         | _                | , -   | -     |

| 2   | 1B  | 1     | 00      | 02               | 04    | 08    |

| 3   | 36  | 0     | 1       | 1                | _     |       |

| 4   | 32  | 1     | 43      | 6D               | 8F    | 09    |

| 5   | 0D  | 1     | 36      | 72               | F0    | 1D    |

| 6   | 31  | 0     | 1 1     | 1 -              | 1     | _     |

| 7   | 16  | 1     | 11      | C2               | DF    | 03    |

| 8   | 24  | 1     | ЗА      | 00               | 51    | 89    |

| 9   | 2D  | 0     | <u></u> | 7                | 1-1   | 1-1   |

| Α   | 2D  | 1     | 93      | 15               | DA    | 3B    |

| В   | 0B  | 0     |         | 1 —              | -     | -     |

| С   | 12  | 0     |         | <sup>1</sup> u — | 1-    | 1-1   |

| D   | 16  | 1     | 04      | 96               | 34    | 15    |

| Ε   | 13  | 1     | 83      | 77               | 1B    | D3    |

| _   | 1/  | 0     |         |                  |       |       |

(c) Cache: 16 sets, 4-byte blocks, direct mapped

| Name: |  |  |  |

|-------|--|--|--|

|       |  |  |  |

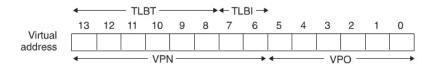

## Class work for Lecture 4/12/2017

Objective: Understand the virtual memory caching process

- The memory is byte addressable.

- Memory accesses are to 1-byte words (not 4-byte words).

- Virtual addresses are 14 bits wide (n = 14).

- Physical addresses are 12 bits wide (m = 12).

- The page size is 64 bytes (P = 64).

- The TLB is 4-way set associative with 16 total entries.

- The L1 d-cache is physically addressed and direct mapped, with a 4-byte line size and 16 total sets.

Show how the memory system on the left translates a virtual address into a physical address and accesses the cache. If there is a cache miss indicate an ? for byte returned

1. What byte is placed in register %rax by this command: mov (\$0x03d4), %rax

2.What byte is placed in register %rax by this command: mov (\$0x03d7), %rax

| mov (\$0x03d4), %rax            | mov (\$0x03d7), %rax                      |  |  |  |  |  |

|---------------------------------|-------------------------------------------|--|--|--|--|--|

| Virtual address format          | Virtual address format                    |  |  |  |  |  |

| 13 12 11 10 9 8 7 6 5 4 3 2 1 0 | 13 12 11 10 9 8 7 6 5 4 3 2 1 0           |  |  |  |  |  |

| Address translation             | Address translation                       |  |  |  |  |  |

| Parameter Value                 | Parameter Value                           |  |  |  |  |  |

| VPN                             | VPN                                       |  |  |  |  |  |

| TLB index                       | TLB index                                 |  |  |  |  |  |

| TLB tag                         | TLB tag                                   |  |  |  |  |  |

| TLB hit? (Y/N)                  | TLB hit? (Y/N)                            |  |  |  |  |  |

| Page fault? (Y/N)               | Page fault? (Y/N)                         |  |  |  |  |  |

| PPN                             | PPN                                       |  |  |  |  |  |

| Physical address format         | Physical address format                   |  |  |  |  |  |

| 11 10 9 8 7 6 5 4 3 2 1 0       | 11 10 9 8 7 6 5 4 3 2 1 0                 |  |  |  |  |  |

| Physical memory reference       | Physical memory reference Parameter Value |  |  |  |  |  |

| Parameter Value                 | Byte offset                               |  |  |  |  |  |

| Byte offset                     | Cache index                               |  |  |  |  |  |

| Cache index                     | Cache tag                                 |  |  |  |  |  |

| Cache tag                       | Cache hit? (Y/N)                          |  |  |  |  |  |

| Cache hit? (Y/N)                | Cache byte returned                       |  |  |  |  |  |

| Cache byte returned             |                                           |  |  |  |  |  |